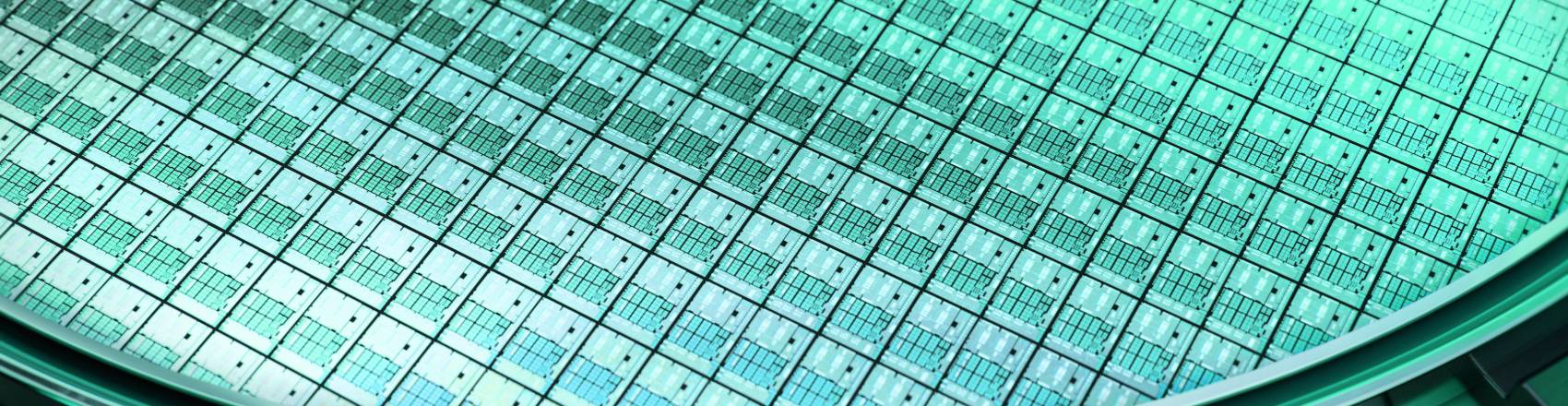

Halbleiter Technologie - Entwicklung und Fertigung

NB Technologies ist Spezialist in der Halbleiter Technologie und bietet Dienstleistungen wie Entwicklung und Fertigung von Halbleiterschaltkreisen.

Elektronik- und Halbleiterunternehmen benötigen Software, die auf Best Practices basiert, die es ihnen ermöglicht, Produkte zu entwickeln und auf den Markt zu bringen.

Ein ganzheitlicher Ansatz ist erforderlich, um kürzere Innovations- und Entwicklungszyklen, eine beschaffungsübergreifende Zusammenarbeit und eine intelligente, integrierte Fertigungsumgebung zu ermöglichen.

Kurze Produktlebenszyklen, Saisonalität in der Nachfrage sowie intensiver Wettbewerb und zunehmende Individualisierung der Endnutzer lassen jedoch wenig Zeit für die Entwicklung optimaler Prozesse in der Elektronikfertigung

(Beispiele für Anwendungen und Branchen, die geeignet sind und die Entwicklung und Fertigung veranschaulichen)

Through Glass Via (TGV)

- Niederohmige Metall-Glas-Durchkontaktierung (<10mOhm)

- Gold- oder Kupfermetallisierung

- Ermöglicht Technologie für Glas-Wafer-Capping für RF- und andere Anwendungen, bei denen eine niedrige Kapazität entscheidend ist

Through Silicon Via (TSV)

- An den Temperaturkoeffizienten angepasste vertikale Durchführung für hohe Zuverlässigkeit

- Hermetische, vakuumdichte elektrische Durchkontaktierung

- Beliebige Form, maximierte Elektrodenfläche

- Siliziumelektrode, keine Metallelektrode erforderlich, vereinfacht das Design und ermöglicht Hochtemperatur-Bonden und Nachbearbeitung

Electroplating

- Galvanisierte Metalle und Lote

- Kosteneffiziente Erzeugung dicker Metallschichten (bis zu 50µm)

- Hochmoderne Galvanikanlagen für die Großserienproduktion

Wafer Bonding

- Mehrere Bonding-Technologien verfügbar

- Schmelzkleben

- Anodisches Kleben

- Eutektisches Kleben

- Thermokompressionskleben

- Polymeres Kleben

- Verpackung auf Wafer-Ebene bei niedrigen Temperaturen (<300°C)

- Funktionelle IR-Kappen mit optischen Beschichtungen, Linsen und Getter

- Lötverbindungen zur Anpassung an die Oberflächentopologie (z. B. CMOS-Wafer)

High Precision RIE

- Multilevel-Strukturen, kombiniert mit Fusionsbonden und SOI-Wafern

- Merkmale mit hohem Aspektverhältnis für Kammantriebsbetätigung und Sensorik

- Hervorragende Dimensionskontrolle von Aufhängungsmerkmalen für Steifigkeitskontrolle und Frequenzspezifikationen in beweglichen Strukturen

- Sehr geringe Seitenwandrauhigkeit für Spiegelanwendungen

Profilkontrolle <1°, Seitenverhältnis bis zu 50:1

AuSn Bumping

- Galvanisch abgeschiedene AuSn-Lote mit hoher Präzision

- Dünne Lote mit ausgezeichneter Dickenkontrolle

- Barriere ermöglicht Null-Ausfluss auf Au-Metallisierung

- Loteigenschaften anpassbar an den Lötprozess